# MOS INTEGRATED CIRCUIT $\mu$ PD16602

## 312-OUTPUT TFT-LCD FULL COLOR DRIVER

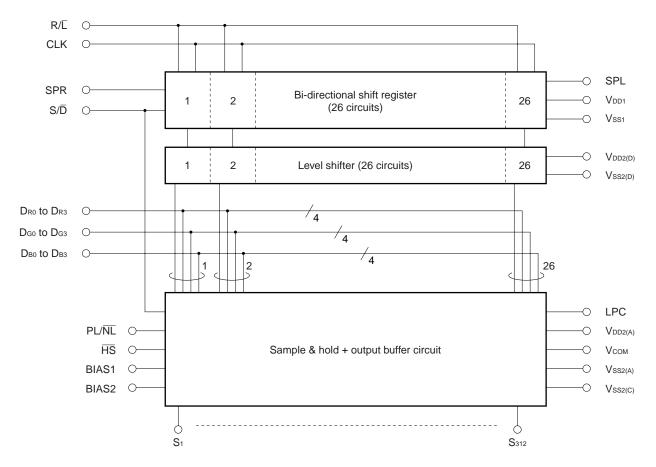

The  $\mu$ PD16602 is a TFT-LCD source driver with full color display capability. It is ideal for 1024 × 768 pixel (XGA) class high definition displays. The internal circuit consists of 12 channels (4 × 3) of analog input pins, 12 channels of 16-bit shift registers and 312 channels of sample & hold circuits (2 latch type).

Analog display signals are sampled in 12 channels simultaneously by the sample & hold circuits and they are output in the next line. The output voltage of the sample & hold circuits is as great as 10.5 VP-P and maintains high accuracy with an output deviation of  $\pm 20 \text{ mV}_{MAX}$ . Inputting analog display signals that been  $\gamma$  -processed in the previous stage signal processing circuit allows realization of a high definition 256-gray-scale-equivalent full color display without requiring line inversion.

#### FEATURES

NEC

- 4 × 3 (RGB)-channel analog input allows display signal input wiring to be reduced.

- High dynamic range (10.0 VP-PMIN. VDD2 = 11.0 V)

- High accuracy sample & hold circuits (output deviation; ±20 mV<sub>MAX.</sub>, ±5.0 mV<sub>TYP.</sub>)

- High-speed sampling frequency (for both analog and digital; fmax. = 20 MHzmin.)

- Low power control (reduction of output buffer bias current) function on chip (operating power consumption; 82 mWTYP., VDD2 = 12.5 V)

- · Bi-directional data store function on chip

- Corresponding to high-density mounting (slim TCP)

#### **ORDERING INFORMATION**

| Part Number                            | Package |

|----------------------------------------|---------|

| $\mu$ PD16602N- $\times \times \times$ | TCP     |

#### 1. BLOCK DIAGRAM

SAMPLE & HOLD + OUTPUT BUFFER CIRCUIT 1

2

#### SAMPLE & HOLD + OUTPUT BUFFER CIRCUIT 2

NEC

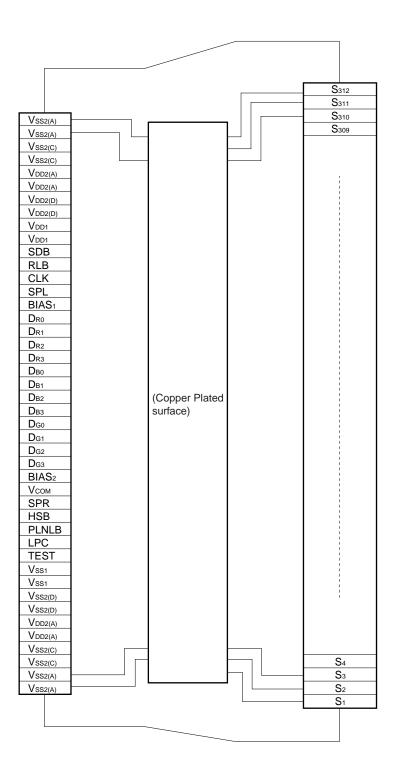

#### 2. PIN CONFIGURATION

#### 3. PIN DESCRIPTION

| Pin Symbol            | Pin Name                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1 to S312            | Driver outputs               | Output pins for sampled analog image signals. When driven with $V_{DD2} = 12.5$ V, a 11.5 V <sub>P-P</sub> analog voltage whose input/output characteristic is gain 1 is output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLK                   | Clock input                  | This pin reads the start pulse at the rising of CLK and starts sampling of analog display signals in 12 channels simultaneously. The active edges of CLK are all rising edges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DR0 to DR3            | Analog display               | Analog image signal input pins. Please input analog display signals by inverting the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DG0 to DG3            | signal inputs                | polarity for each display line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DB0 to DB3            |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| R/Ī                   | Shift direction              | The shift direction of the shift register is as follows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | switching input              | $ \begin{array}{ll} R/\overline{L} = H \mbox{ (right shift) }; & SPR \mbox{ input, } S_1 \to S_{312}, \mbox{ SPL output} \\ R/\overline{L} = L \mbox{ (left shift) }; & SPL \mbox{ input, } S_{312} \to S_1, \mbox{ SPR output} \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SPR                   | Start pulse input/           | R/L = H (right shift); start pulse input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | output                       | R/L = L (left shift) ; start pulse output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPL                   | Start pulse input/<br>output | R/L = H (right shift); start pulse output pin<br>R/L = L (left shift); start pulse input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

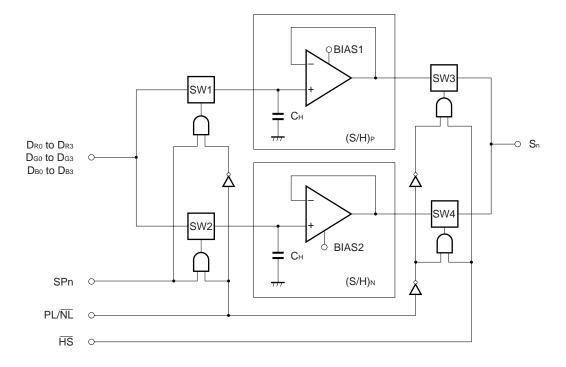

| PL/NL <sup>Note</sup> | Polarity inversion<br>input  | <ul> <li>S/D = L; When PL/NL = H, Both odd number pin and even number pin samples negative analog display signals and outputs positive analog signals from the driver output.</li> <li>When PL/NL = L, Both odd number pin and even number pin samples positive analog display signals and outputs negative analog signals from the driver output.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       |                              | <ul> <li>S/D = H; When PL/NL = H, Odd number pin samples negative analog display signals and outputs positive analog signals from the driver output. Even number pin samples positive analog display signals and outputs negative analog signals from the driver output.</li> <li>When PL/NL = L, Odd number pin samples positive analog display signals and outputs negative analog signals from the driver output. Even number pin samples negative analog signals and outputs negative analog signals from the driver output. Even number pin samples negative analog display signals and outputs negative analog signals from the driver output. Even number pin samples negative analog display signals and outputs positive analog signals from the driver output.</li> </ul> |

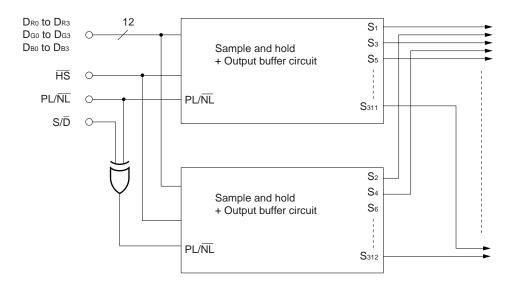

| S/D                   | Arrangement switching input  | $S/\overline{D} = H$ ; Complying with one side arrangement dot inverting.<br>$S/\overline{D} = L$ ; Complying with both sides arrangement dot inverting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HS <sup>Note</sup>    | Horizontal synchronous input | This pin shuts off the output at the falling edge and then outputs analog display signals at the rising. When $\overline{HS} = L$ , after the driver output pin goes to high impedance this pin switches $PL/\overline{NL}$ and resets the internal hold capacity and output buffer to the V <sub>COM</sub> level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LPC                   | Low power control input      | This pin shuts off the output buffer low current supply and increases the output impedance. The LPC = "H" mode allows the static current consumption to be reduced by approximately 20 %.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIAS1<br>BIAS2        | Bias voltage inputs          | These pins control the current consumption of the output buffer by applying a stabilized external power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDD1                  | Logic power supply           | 3.3 V ±0.3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDD2(D)               | Driver power supply          | 13.5 Vmax.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VDD2(A)               | Driver power supply          | 13.5 Vmax.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Vсом                  | Common power<br>supply       | This pin applies the intermediate voltage of a stable LCD drive voltage from a voltage follower, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Vss1                  | Logic ground                 | Logic ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Vss2(D)               | Driver ground                | High voltage block (level shifter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSS2(A)               | Driver ground                | High voltage block (output buffer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSS2(C)               | Driver ground                | High voltage block (sample & hold)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TEST                  | Test pin                     | "L" or left open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

**Note** Sample & hold operation and reset operation of the output buffer capacitance and V<sub>COM</sub> level are performed by the PL/NL and HS logic.

#### 4. NOTES ON USE

(1) In order to prevent latch up breakdown, power should be applied in the order of:

$V_{DD1} \rightarrow \text{logic input} \rightarrow V_{DD2(D), (A)} \rightarrow V_{BIAS1,2}, V_{COM} \rightarrow \text{analog display signal input, and turned off in the reverse order.}$

This order should also be observed in transition periods.

(2) Vss1, Vss2(D), Vss2(A) and Vss2(C) are connected in the diffusion layer, but also be sure to connect them externally.

Do not share the sample & hold ground Vss2(c) with other ground wiring on the mount board, but connect it to the edge to the signal board. There is a possibility of high-voltage or logic type noise being superimposed onto the sample & hold circuit, damaging the analog characteristics (output deviation, etc.).

- (3) Likewise, to prevent the sample & hold characteristics from deteriorating, insert a bypass capacitor of 0.1 μF between V<sub>DD1</sub> and V<sub>SS1</sub>, and approximately 0.1 μF between V<sub>DD2(D)</sub>, (A) and V<sub>SS2(D)</sub>, (A). An unstable power supply may cause a driver through current, preventing the output range of the output buffer from being sufficiently secured. Therefore, determine the capacitance of the bypass capacitor after a thorough evaluation.

- (4) When LPC = "H", stable current supply of the output buffer may be shut off, which will impede normal negative feedback, and when the LCD panel load is small, the output voltage may become abnormal. Normal operation is assured with approximately 10 kΩ + 50 pF, but when the time constant is smaller than this, please set LPC = "L".

#### (5) Data input/output relationship

As shown below, irrespective of right shift and left shift.

| Output | S1  | S <sub>2</sub> | S₃              | S4              | S₅              | S <sub>6</sub> | <b>S</b> 309    | <b>S</b> 310 | <b>S</b> 311 | <b>S</b> 312 |

|--------|-----|----------------|-----------------|-----------------|-----------------|----------------|-----------------|--------------|--------------|--------------|

| Data   | Dro | Dво            | D <sub>G0</sub> | D <sub>R1</sub> | D <sub>B1</sub> | DG1            | D <sub>G2</sub> | Dr3          | Dвз          | Dg3          |

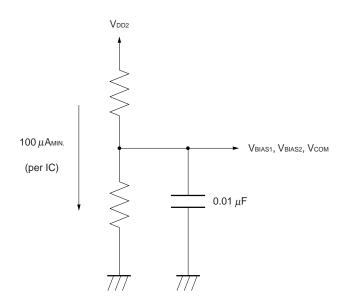

#### (6) Bias control method

Externally applying a voltage to pins BIAS<sub>1</sub> and BIAS<sub>2</sub> can control the output buffer current consumption. In this case, the analog characteristics (output deviation, driving capability, response speed, etc.) will not change. Please refer to the configuration in the figure below for the actual circuit. Also refer to the same configuration for the V<sub>COM</sub> voltage input circuit. Current per driver IC is as follws.

#### 5. FUNCTIONAL DESCRIPTION

|     |       |                 | Display signal input terminal/Output terminal |                             |                 |  |                 |                  |                  |                  |  |  |

|-----|-------|-----------------|-----------------------------------------------|-----------------------------|-----------------|--|-----------------|------------------|------------------|------------------|--|--|

| S/D | PL/NL | DR0<br>S12n + 1 | Dво<br>S12n + 2                               | Dgo<br>S <sub>12n</sub> + 3 | DR1<br>S12n + 4 |  | Dg2<br>S12n + 9 | DR3<br>S12n + 10 | Dвз<br>S12n + 11 | DG3<br>S12n + 12 |  |  |

| н   | Н     | (—)             | (+)                                           | (—)                         | (+)             |  | ()              | (+)              | (—)              | (+)              |  |  |

|     | L     | (+)             | (—)                                           | (+)                         | (—)             |  | (+)             | (—)              | (+)              | ()               |  |  |

| L   | Н     | (—)             | (—)                                           | (—)                         | ()              |  | ()              | (—)              | ()               | ()               |  |  |

|     | L     | (+)             | (+)                                           | (+)                         | (+)             |  | (+)             | (+)              | (+)              | (+)              |  |  |

#### (1) Input Specification of the analog display signal (n = 0 to 25, R/L = "H" or "L")

(+) : Please input the positive analog input signal.

(-) : Please input the negative analog input signal.

#### (2) Output Specification of the analog display signal

• Single Bank Arrangement for dot inversion  $(S/\overline{D} = "H")$ Polarity of the output voltage

| Line No. | PL/NL | S1 (DR0) | S2 (DR0) | S3 (DG0) | S4 (DR1) | S5 (DB1) | S6 (DG1) | S7 (DR2) |  |

|----------|-------|----------|----------|----------|----------|----------|----------|----------|--|

| 1        | Н     | (+)      | (—)      | (+)      | (—)      | (+)      | (—)      | (+)      |  |

| 2        | L     | (—)      | (+)      | (—)      | (+)      | (—)      | (+)      | (—)      |  |

| 3        | н     | (+)      | (—)      | (+)      | (—)      | (+)      | (—)      | (+)      |  |

| 4        | L     | (—)      | (+)      | (—)      | (+)      | (—)      | (+)      | (—)      |  |

| 5        | н     | (+)      | (-)      | (+)      | (-)      | (+)      | (-)      | (+)      |  |

(+) : Positive analog output (Negative line sampling), (-) : Negative analog output (Positive line sampling)

|          | Input sign | al polarity | Output Polarity of the upper driver IC's |                 |                |                     |             |               |                |               |

|----------|------------|-------------|------------------------------------------|-----------------|----------------|---------------------|-------------|---------------|----------------|---------------|

| Line No. | PL         | /NL         | S1                                       | $\overline{\ }$ | S <sub>2</sub> |                     | S₃          | $\backslash$  | S4             | $\backslash$  |

|          | Upper side | Lower side  | (Dro)                                    |                 | (Dво)          |                     | (DG0)       |               | (DR1)          |               |

| 1        | Н          | L           | (+)                                      | (–)             | (+)            | (–)                 | (+)         | (-)           | (+)            | (-)           |

| 2        | L          | Н           | (-)                                      | (+)             | (-)            | (+)                 | (-)         | (+)           | (-)            | (+)           |

| 3        | Н          | L           | (+)                                      | (–)             | (+)            | (–)                 | (+)         | (-)           | (+)            | (-)           |

| 4        | L          | н           | (—)                                      | (+)             | (-)            | (+)                 | (—)         | (+)           | (—)            | (+)           |

|          |            |             |                                          | -               |                |                     |             |               |                |               |

| 767      | Н          | L           | (+)                                      | (–)             | (+)            | (-)                 | (+)         | (-)           | (+)            | (-)           |

| 768      | L          | Н           | (–)                                      | (+)             | (-)            | (+)                 | (-)         | (+)           | (-)            | (+)           |

|          | _          |             | $\overline{\ }$                          | <b>S</b> 312'   |                | <b>S</b> 311'       |             | <b>S</b> 310' | $\overline{\}$ | <b>S</b> 309' |

|          |            | _           |                                          | (DG3')          |                | (D <sub>B3'</sub> ) |             | (Dr3')        |                | (Dg2')        |

|          |            |             |                                          |                 | Output p       | olarity of t        | he lower dr | iver IC's     |                |               |

### • Dual Bank Arrangement for dot inversion (S/ $\overline{D}$ = "L")

Polarity of the each output voltage

Sn : Output voltage of the upper side driver,

(+) : Positive output of the upper side driver

Sn': Output voltage of the lower side driver,

(-) : Negative output of the lower side driver

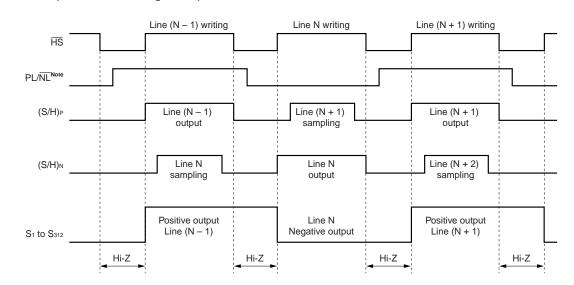

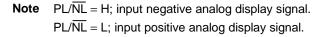

(3) Sampling and hold timing  $(R/\overline{L} = "L")$ S/ $\overline{D} = "L"$  (Dual Bank Arrangement)

#### S/D = "H" (Single Bank Arrangement)

NoteOdd number pin $PL/\overline{NL} = H$ ; input negative analog display signal. $PL/\overline{NL} = L$ ; input positive analog display signal.Even number pin $PL/\overline{NL} = H$ ; input positive analog display signal. $PL/\overline{NL} = L$ ; input negative analog display signal. $PL/\overline{NL} = L$ ; input negative analog display signal.

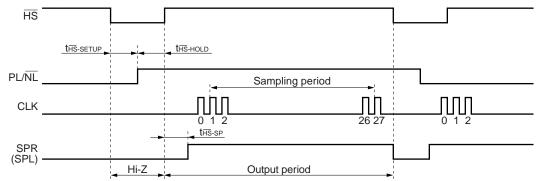

(4) Relatonship with  $\overline{\text{HS}}$  and  $\text{PL}/\overline{\text{NL}}$

#### Caution HS and PL/NL edges have no relationship with clock timing.

| Timing Item                           | Symbol                 | Description                                                                                                                                                                                                                   |

|---------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Horizontal synchronization setup time | t <del>hs</del> -setup | Setup time of PL/NL signal with respect to HS.<br>Secure 50 nsmin. at least.                                                                                                                                                  |

| Horizontal synchronization hold time  | t <del>HS</del> -HOLD  | PL/NL hold time. Secure 250 nsmn. at least.<br>The hold capacitance at this time is at common potential V <sub>COM</sub> , but the output<br>buffer does not reach V <sub>COM</sub> , and therefore sampling is not possible. |

| Sampling start time                   | t <del>HS</del> -SP    | Time for the output buffer to reach V <sub>COM</sub> (reset level).<br>Secure 1.0 $\mu$ <sub>SMIN</sub> at least. Sampling is possible at this time.<br>Input the start pulse at this time.                                   |

These characteristics are specified by load constants of 50 k $\Omega$  + 100 pF.

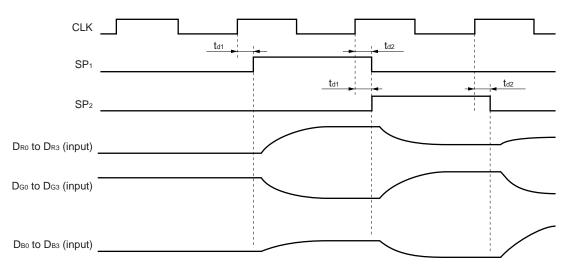

#### (5) Internal sampling delay

| Timing Duration          | Symbol | Description                                                                                                                                                                                    |

|--------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK-sampling pulse delay | ta1    | Delay time between CLK signal and rising edge of internal sampling pulse SPn.<br>Input an analog image signal with a timing difference of td1 in order to secure a sufficient sampling period. |

| Sampling pulse-CLK delay | td2    | Delay time between CLK signal and falling edge of internal sampling pulse.                                                                                                                     |

$t_{d1}$  is 22 ±5 ns and  $t_{d2}$  is 14 ±5 ns (these are not guaranteed values).

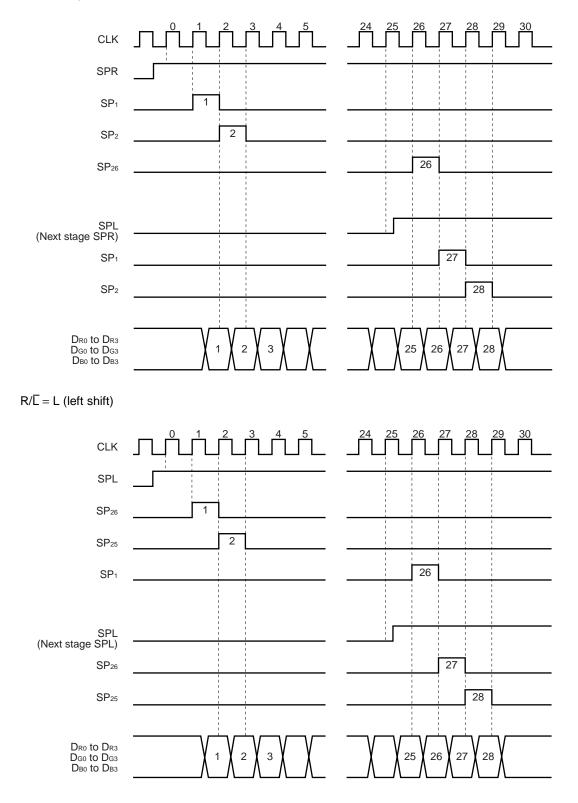

#### (6) Cascade timing

R/L = H (right shift)

#### 6. ELECTRIC SPECIFICATION

#### ABSOLUTE MAXIMUM RATINGS (TA = $25^{\circ}$ C, Vss(D), (A), (C) = 0 V)

| Item                         | Symbol          | Rating            | Unit |

|------------------------------|-----------------|-------------------|------|

| Logic supply voltage         | VDD1            | -0.5 to +6.5      | V    |

| Logic input voltage          | Vin             | -0.5 to VDD1 +0.5 | V    |

| Logic output voltage         | V <sub>01</sub> | -0.5 to VDD1 +0.5 | V    |

| Driver supply voltage        | Vdd2 (d), (a)   | –0.5 to +15       | V    |

| Display signal input voltage | VIN (A)         | -0.5 to VDD2 +0.5 | V    |

| Driver output voltage        | V <sub>02</sub> | -0.5 to VDD2 +0.5 | V    |

| Driver output current        | lo2             | ±10               | mA   |

| Operating temperature range  | TA              | -10 to +75        | °C   |

| Storage temperature range    | Tstg            | -40 to +125       | °C   |

#### **RECOMMENDED OPERATING RANGE** $(T_A = -10 \text{ to } 75^{\circ}\text{C}, V_{SS} = 0 \text{ V})$

| Item                     | Symbol   | MIN.      | TYP.      | MAX.      | Unit |

|--------------------------|----------|-----------|-----------|-----------|------|

| Logic supply voltage     | Vdd1     | 3.0       | 3.3       | 3.6       | V    |

| High-level input voltage | Vін      | 0.7 Vdd1  |           |           | V    |

| Low-level input voltage  | VIL      |           |           | 0.3 Vdd1  | V    |

| Driver supply voltage    | Vdd2     | 11.0      | 12.5      | 13.5      | V    |

| Display signal input     | Vin (A)  | Vss +0.5  |           | Vdd2 -0.5 | V    |

| Driver output voltage    | Vo       | Vss +0.5  |           | Vdd2 -0.5 | V    |

| Bias current             | BIAS1, 2 | 100       |           |           | μ Α  |

| Bias voltage             | VBIAS1   | Vss +4.5  | Vss +5.0  | Vss +5.5  | V    |

|                          | VBIAS2   | Vdd2 -7.5 | Vdd2 -7.0 | Vdd2 -6.5 | V    |

| Item                                | Symbol | Cond                                                | MIN.                             | TYP. | MAX. | Unit |    |

|-------------------------------------|--------|-----------------------------------------------------|----------------------------------|------|------|------|----|

| High-level output voltage           | Vон    | Logic, IOH1 = 0 mA                                  | VDD1 -0.1                        |      |      | V    |    |

| Low-level output voltage            | Vol    | Logic, IoL1 = 0 mA                                  |                                  |      |      | 0.1  | V  |

| Input leakage current               | liL    | Vi = VDD1, VSS1                                     |                                  |      |      | ±10  | μA |

| Driver output current (black level) | ОН11   | $PL/\overline{NL} = H$ (source)                     | $V_{R} = V_{G} = V_{B} = 11 \ V$ |      |      | -0.3 | mA |

| Driver output current (white level) | Іон12  | Vo = 3.0 V                                          | $V_{R} = V_{G} = V_{B} = 7 \ V$  |      |      | -0.3 | mA |

| Driver output current (white level) | Іон21  | $PL/\overline{NL} = L (sink)$                       | $V_{R} = V_{G} = V_{B} = 5 \ V$  | 0.3  |      |      | mA |

| Driver output current (black level) | Іон22  | Vo = 9.0 V                                          | $V_R = V_G = V_B = 1 \ V$        | 0.3  |      |      | mA |

| Output off leakage current          | IOFF   | Vo2 = Vdd2, Vss                                     |                                  |      | ±1   | μA   |    |

| Dynamic current consumption         | DD12   | Vdd1, fclk = 20 MHz                                 |                                  | 0.3  | 0.8  | mA   |    |

|                                     | IDD22  | VDD2, fHS = 66 kHz, LP                              |                                  | 9.5  | 15   | mA   |    |

|                                     |        | VDD2, fHS = 66 kHz, LP                              | C = H, No load                   |      | 6.5  | 13   | mA |

| Static current consumption          | DD21   | V <sub>DD2</sub> , No load<br>fਜs = 66 kHz, LPC = L | VDD2, No load                    |      |      |      | mA |

|                                     |        | V <sub>DD2</sub> , No load<br>fਜs = 66 kHz, LPC = H |                                  | 6.0  | 12   | mA   |    |

| Note<br>Output deviation            | ΔVo    | $V_R = V_G = V_B = 7$ to 11                         | V, $PL/\overline{NL} = H$        |      | ±5.0 | ±20  | mV |

|                                     |        | $V_{R} = V_{G} = V_{B} = 1 \text{ to } 5 \text{ V}$ | $', PL/\overline{NL} = L$        |      | ±5.0 | ±20  | mV |

# ELECTRICAL SPECIFICATIONS (T<sub>A</sub> = -10 to 75°C, V<sub>DD1</sub> = 3.3 V ±0.3 V, V<sub>DD2</sub> =12.5 $^{+1.0}_{-1.5}$ V, V<sub>SS</sub> = 0 V)

**Note** The "deviation" indicates the minimum and maximum values in the driver output voltage distribution in the chip.

| ltem                          | Symbol | Condition                                             | MIN. | TYP. | MAX. | Unit |

|-------------------------------|--------|-------------------------------------------------------|------|------|------|------|

| Start pulse output delay time | tPLH1  | CL = 20 pF                                            | 12   | 20   | 40   | ns   |

| Driver output delay time      | tPHL2  | $C_L = 50 \text{ pF}, \text{ R} = 50 \text{ k}\Omega$ |      | 6.75 | 11   | μs   |

|                               | tphL3  |                                                       |      | 13.5 | 17   | μs   |

|                               | tPLH2  |                                                       |      | 6.75 | 11   | μs   |

|                               | tрLH3  |                                                       |      | 13.5 | 17   | μs   |

| Input capacitance             | Ci1    | Logic except for SPR (SPL), $T_A = 25^{\circ}C$       |      | 7    | 10   | pF   |

|                               | Ci2    | SPR (SPL), T <sub>A</sub> = 25°C                      |      | 10   | 15   | pF   |

|                               | Сіз    | Display signal input pin                              |      | 20   |      | pF   |

| Maximum clock frequency       | fmax.  |                                                       | 20   |      |      | MHz  |

## SWITCHING CHARACTERISTICS (T<sub>A</sub> = -10 to +75°C, V<sub>DD1</sub> = 3.3 V ±0.3 V, V<sub>DD2</sub> =12.5 $^{+1.0}_{-1.5}$ V, V<sub>SS</sub> = 0 V)

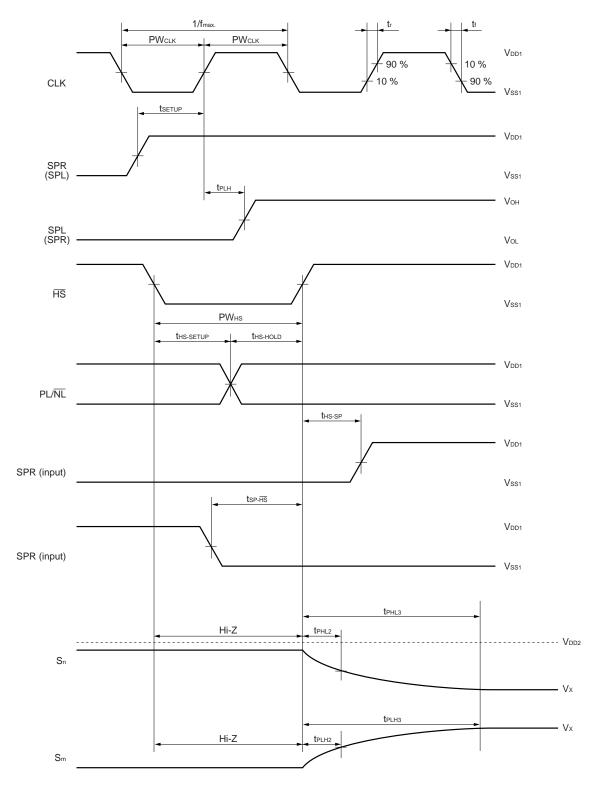

#### TIMING REQUIREMENT (TA = -10 to +75°C, VDD1 = $3.3 \text{ V} \pm 0.3 \text{ V}$ , Vss = 0 V, tr = tr = 5 ns)

| Item                                      | Symbol              | Condition   | MIN. | TYP. | MAX. | Unit |

|-------------------------------------------|---------------------|-------------|------|------|------|------|

| Clock pulse width                         | PWclk               | Duty = 50 % | 25   |      |      | ns   |

| Horizontal synchronous signal pulse width | PWHS                |             | 300  |      |      | ns   |

| Start pulse setup time                    | <b>t</b> SETUP      |             | 10   |      |      | ns   |

| CLK-sampling pulse delay time             | t <sub>d1</sub>     |             |      | 15   |      | ns   |

| Sampling pulse-CLK delay time             | td2                 |             |      | 15   |      | ns   |

| Horizontal synchronous signal setup time  | tHS-SETUP           |             | 50   |      |      | ns   |

| Horizontal synchronous signal hold time   | tHS-HOLD            |             | 250  |      |      | ns   |

| HS-start pulse time                       | t <del>H</del> S-SP |             | 1.0  |      |      | μs   |

| Start pulse-HS time                       | tsp-HS              |             | 10   |      |      | ns   |

#### SWITCHING CHARACTERISTICS $(R/\overline{L} = H)$

Items in ( ) apply when  $R/\overline{L} = L$ .

Unless otherwise specified, the input levels are all set to 0.5  $V_{\text{DD1}}$

Vx refers to the final output voltage, tPLH2 and tPHL2 refer to the time required to an output precision level of 10 % (0.1 Vx); and tPLH3 and tPHL3 refer to the time required to reach an output precision level of 6 bits.

#### **RECOMMENDED MOUNTING CONDITIONS**

When mounting this product, please make sure that the following recommended conditions are satisfied.

For packaging methods and conditions other than those recommended below, please contact NEC sales personnel.

| Mounting Condition | Mounting Method                | Condition                                                                                                                                                                                                                                                                   |

|--------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermocompression  | Soldering                      | Heating tool 300 to 350°C, heating for 2 to 3 seconds; pressure 100 g (per solder)                                                                                                                                                                                          |

|                    | ACF (Adhesive Conductive Film) | Temporary bonding 70 to 100°C; pressure 3 to 8 kg/cm <sup>2</sup> ;<br>time 3 to 5 secs.<br>Real bonding 165 to 180°C; pressure 25 to 45 kg/cm <sup>2</sup> , time<br>30 to 40 secs. (When using the anisotropic conductive<br>film SUMIZAC1003 of Sumitomo Bakelite, Ltd.) |

## Caution To find out the detailed conditions for packaging the ACF part, please contact the ACF manufacturing company. Be sure to avoid using two or more packaging methods at a time.

#### Reference

NEC Semiconductor Device Reliability/Quality Control System (IEI-1212) Quality Grades on NEC Semiconductor Devices (C11531E) No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.